- Home

- About Us

- Our Services

- Parts Screening & Testing

- EEE Parts Management

- Destructive Physical & Failure Analysis

- Counterfeit Parts Analysis, Screening, & Detection

- RF Testing, Screening, & Qualification

- Custom Assembly, Packaging & Qualification

- Patented DPEM Process for Die Removal

- Cryogenics Test Lab

- Trusted Semiconductor Die/Wafer Source

- QML Memory

- Obsolete Parts Replacement

- Quality

- News

- Contact

- Search

Call Us Today!: 805-581-9200

Call Us Today!: 805-581-9200

- Home

- About Us

- Our Services

- Parts Screening & Testing

- EEE Parts Management

- Destructive Physical & Failure Analysis

- Counterfeit Parts Analysis, Screening, & Detection

- RF Testing, Screening, & Qualification

- Custom Assembly, Packaging & Qualification

- Patented DPEM Process for Die Removal

- Cryogenics Test Lab

- Trusted Semiconductor Die/Wafer Source

- QML Memory

- Obsolete Parts Replacement

- Quality

- News

- Contact

- Search

- Home

- About Us

- Our Services

- Parts Screening & Testing

- EEE Parts Management

- Destructive Physical & Failure Analysis

- Counterfeit Parts Analysis, Screening, & Detection

- RF Testing, Screening, & Qualification

- Custom Assembly, Packaging & Qualification

- Patented DPEM Process for Die Removal

- Cryogenics Test Lab

- Trusted Semiconductor Die/Wafer Source

- QML Memory

- Obsolete Parts Replacement

- Quality

- News

- Contact

- Search

Risk Analysis

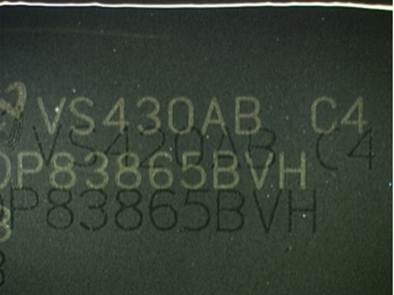

DPACI has performed risk analysis on each screening process method under MIL-STD-883 and MIL-STD-750 based on its capability to independently distinguish an authentic from a counterfeit device. Each test process was analyzed to determine its effective percent coverage to the overall device characteristics and properties for the device under test. A value for a Counterfeit Detection Confidence (CDC) is determined based on each test Process Cycle Time (PCT) and its Effective Detection Coverage (EDC) to the overall device characteristics and properties for the device under test in RISK ANALYSIS. In order to achieve a suitable set of tests to yield the highest percent of device characteristics/properties coverage for a best cycle time, DPACI proposed the following optimized test plans in two phases.

RISK ANALYSIS MATRIXES

The next section are risk analysis matrixes to determine the Counterfeit Detection Confidence (CDC) of digital, linear, mix signal microcircuits and discrete semiconductors, based on the Process Cycle Time (PCT) and the Effective Detection Coverage (EDC) of the device characteristics and properties for each Test Process.

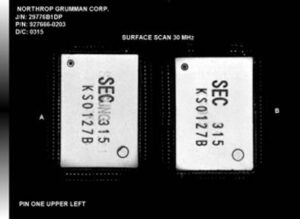

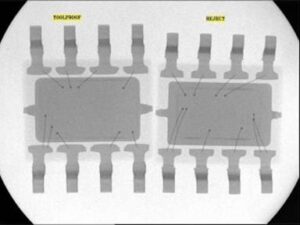

PHASE 1 SCREENING

The Phase I Flow is optimized to a near 100% confidence level of authenticity if the parts are 100% screened and 100% passed. If any counterfeit or anomalies are found in Phase I, Phase II Flow may be invoked on a 5 piece sample for destructive testing and then the lot is 100% screened to the screening flow of Figure E-1 in AS5553 for further scrutiny of the part’s authenticity.